# MOS INTEGRATED CIRCUIT $\mu PD6708$

## IEBus™ (Inter Equipment Bus™) PROTOCOL CONTROL LSI

#### DESCRIPTION

The  $\mu$ PD6708 is a peripheral LSI for microcontrollers that controls the protocol of the IEBus.

This LSI processes the protocol of the IEBus. Because it is provided with a transmit/receive buffer, the microcontroller can concentrate on the application processing of the IEBus. Because the  $\mu$ PD6708 also contains an IEBus driver/receiver, it can be directly connected to the bus.

#### **FEATURES**

- Protocol control of IEBus

- Multi-master system

- Broadcast communication function (communication between one unit and multiple units)

- Choice of three modes with different transmission speeds

|        | At 12 MHz        | At 12.58 MHz     |

|--------|------------------|------------------|

| Mode 0 | Approx. 3.9 Kbps | Approx. 4.1 Kbps |

| Mode 1 | Approx. 17 Kbps  | Approx. 18 Kbps  |

| Mode 2 | Approx. 26 Kbps  | Approx. 27 Kbps  |

- On-chip IEBus driver/receiver

- Transmit/receive buffer Transmit: 4-byte FIFO Receive: 20-byte FIFO

- Interface with microcontroller

- Three-line serial I/O (SCK, SO, SI pins)

- Transfer with MSB first

- Oscillation frequency (fx): 12 MHz, 12.58 MHz

- In modes 0 and 1:  $\pm 1.5$  %

- In mode 2: ±0.5 %

- Supply voltage: VDD = 5 V ±10 %

#### **ORDERING INFORMATION**

| Part Number    | Package                      |

|----------------|------------------------------|

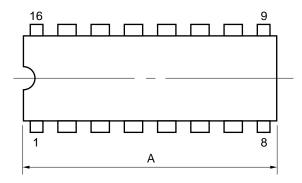

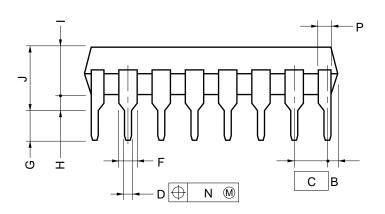

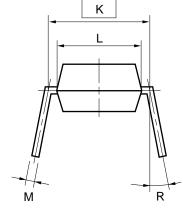

| μPD6708CX      | 16-pin plastic DIP (300 mil) |

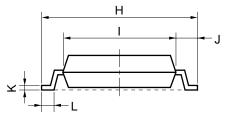

| $\mu$ PD6708GS | 16-pin plastic SOP (300 mil) |

#### **APPLICATION FIELD**

Fields where a small-scale digital data transfer system is required between equipment, such as automobile electronic systems and industrial equipment

The information in this document is subject to change without notice.

#### PIN CONFIGURATION (TOP VIEW)

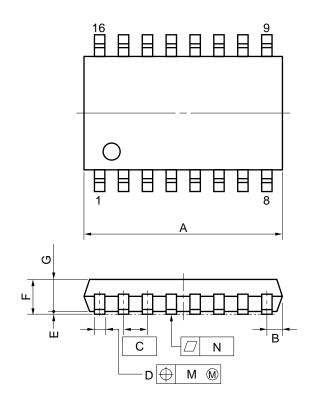

- 16 pin plastic DIP (300 mil) μPD6708CX

- 16 pin plastic SOP (300 mil) μPD6708GS

| SCK        | : Serial clock input                               |

|------------|----------------------------------------------------|

| SI         | : Serial data input                                |

| SO         | : Serial data output                               |

| IRQ        | : Interrupt request output                         |

| R/W        | : Read/write switchover input                      |

| XI, XO     | : System clock                                     |

| GND        | : Ground                                           |

| BUS-, BUS+ | : IEBus input/output                               |

| AVdd       | : IEBus analog power supply (connected to VDD pin) |

| C/D        | : Command/data switchover input                    |

| CS         | : Chip select input                                |

| RESET      | : Reset input                                      |

| TEST       | : Test input (connected to VDD pin)                |

| Vdd        | : Positive power supply                            |

|            |                                                    |

## CONTENTS

| 1. | <b>PIN</b><br>1.1 | UNCTIONS<br>List of Pin Functions                     | -   |

|----|-------------------|-------------------------------------------------------|-----|

| 2. | IEBu              | s OPERATION                                           | . 6 |

|    | 2.1               | Operation Overview                                    |     |

|    | 2.2               | IEBus Communication Protocol                          |     |

|    |                   | 2.2.1 Bus mastership determination (arbitration)      |     |

|    |                   | 2.2.2 Communication modes                             | . 8 |

|    |                   | 2.2.3 Communication address                           | 9   |

|    |                   | 2.2.4 Broadcast communication                         | 9   |

|    | 2.3               | Transfer Protocol                                     |     |

|    | 2.4<br>2.5        | Transfer Data (Contents of Data Field)<br>Bit Format  |     |

|    | 2.5               | Bit Format                                            | 19  |

| 3. | INTE              | RNAL CONFIGURATION                                    | 20  |

|    | 3.1               | Data Link Layer Controller                            |     |

|    | 3.2               | Physical Layer Controller                             |     |

|    | 3.3<br>3.4        | IEBus Driver/Receiver Host Interface                  |     |

|    | 3.4               | Host Interface                                        | 21  |

| 4. | INTE              | RFACING WITH HOST CONTROLLER                          |     |

|    | 4.1               | Accessible Buffers and Registers from Host Controller |     |

|    |                   | 4.1.1 Write data buffer (WDB)                         |     |

|    |                   | 4.1.2 Read data buffer (RDB)                          |     |

|    |                   | 4.1.3 Command register (CMR)                          |     |

|    |                   | 4.1.4 Status register (STR)                           | 23  |

|    | 4.2               | Host Interface Modes                                  |     |

|    |                   | 4.2.1 Switching through pin control                   |     |

|    |                   | 4.2.2 Switching through software control              |     |

|    | 4.3               | Reset Mode                                            | 28  |

| 5. | CON               | MUNICATION CONTROL COMMANDS                           | 30  |

|    | 5.1               | Overview of Communication Control Commands            |     |

|    | 5.2               | Communication Control Command Functions               |     |

|    |                   | 5.2.1 INIT command (command code: 0000)               |     |

|    |                   | 5.2.2 SETSA command (command code: 0001)              |     |

|    |                   | 5.2.3 MREQ1 command (command code: 0010)              |     |

|    |                   | 5.2.4 MREQ2 command (command code: 0011)              |     |

|    |                   | 5.2.5 ABORT command (command code: 0100)              | 34  |

|    |                   | 5.2.6 SETSD command (command code: 0101)              | 35  |

|    |                   | 5.2.7 GETSTA command (command code: 0110)             | 36  |

|    |                   | 5.2.8 SETREV command (command code: 0111)             | 37  |

| 6. | DET               | JRN CODES                                             | 20  |

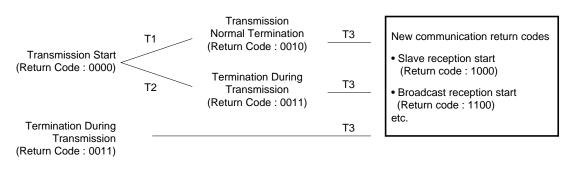

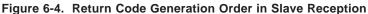

| 0. | 6.1               | Return Codes in Master/Slave Data Transmission        |     |

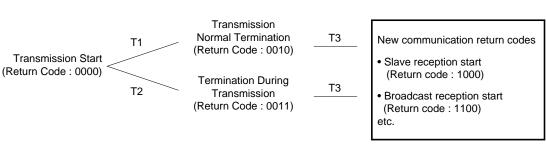

|    | 6.2               | Return Codes in Master Reception                      |     |

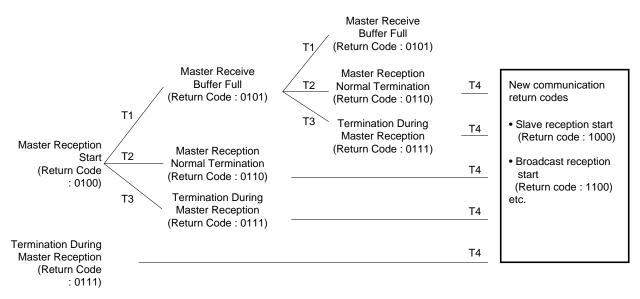

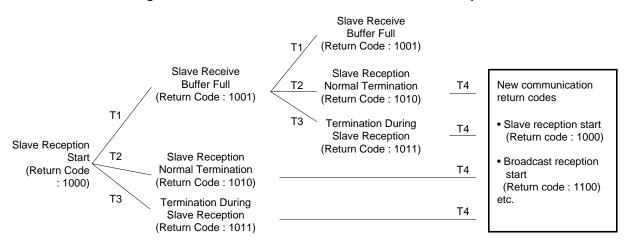

|    | 6.3               | Return Codes in Slave Reception                       | 39  |

|    | 6.4               | Return Codes in Broadcast Reception                   |     |

|    | 6.5               | Return Codes Generation Intervals                     | 40  |

| 7. | CON               | MUNICATING WITH HOST CONTROLLER                       | 43  |

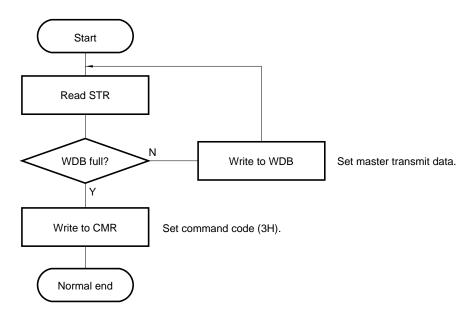

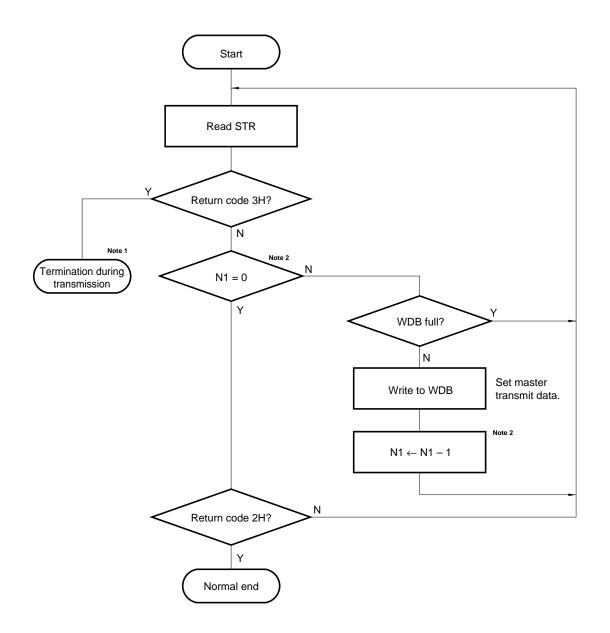

|    | 7.1               | Master Transmission                                   |     |

|    |                   | 7.1.1 Master transmission by MREQ1 command            | 43  |

|    |                   | 7.1.2 Master transmission by MREQ2 command            | 44  |

|    |                   |                                                       |     |

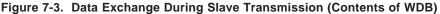

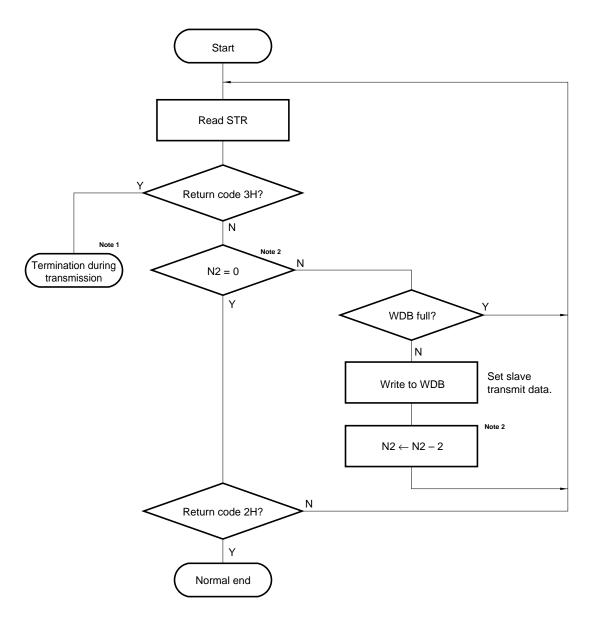

|     | 7.2  | Slave T  | ransmission                                                             |    |

|-----|------|----------|-------------------------------------------------------------------------|----|

|     |      | 7.2.1    | Data transmission                                                       | 44 |

|     |      | 7.2.2    | Transmitting slave status address and lock address                      |    |

|     | 7.3  | Master   | Reception                                                               | 45 |

|     | 7.4  | Slave R  | eception                                                                | 46 |

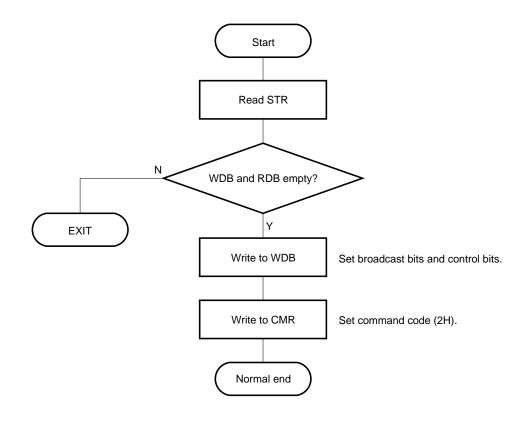

|     | 7.5  | Broadca  | ast Reception                                                           | 47 |

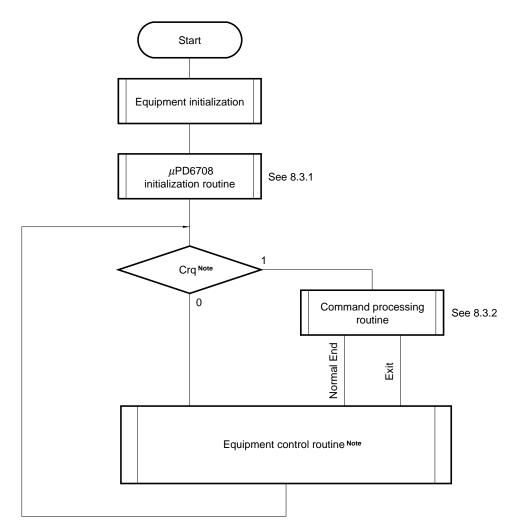

| 8.  | FYΔ  |          | F HOST CONTROLLER PROCESSING FLOW                                       | 18 |

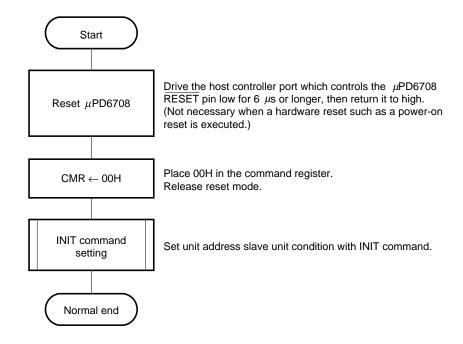

| 0.  | 8.1  |          | butine                                                                  |    |

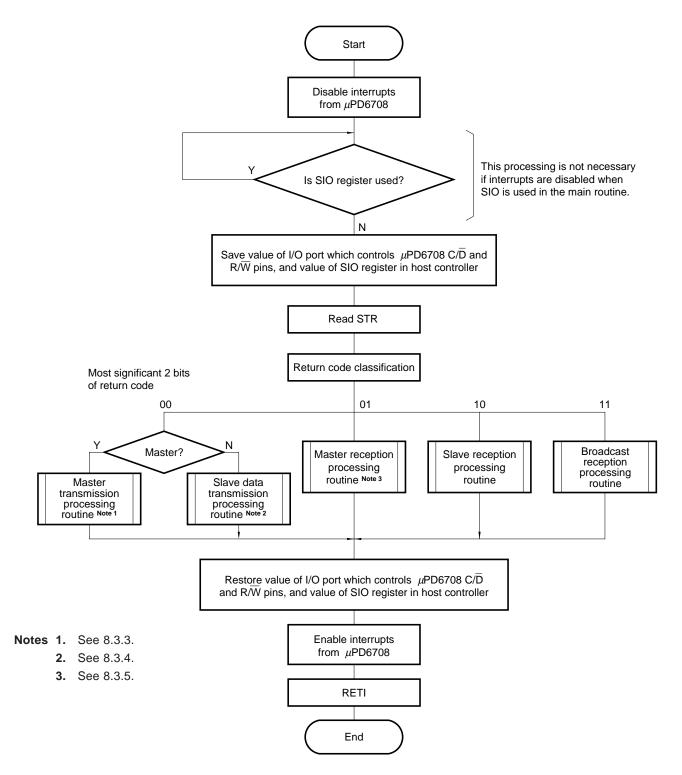

|     | 8.2  | Interrup | t Service Routine                                                       | 49 |

|     | 8.3  |          | sing Routine                                                            | 50 |

|     |      | 8.3.1    | $\mu$ PD6708 initialization routine                                     | 50 |

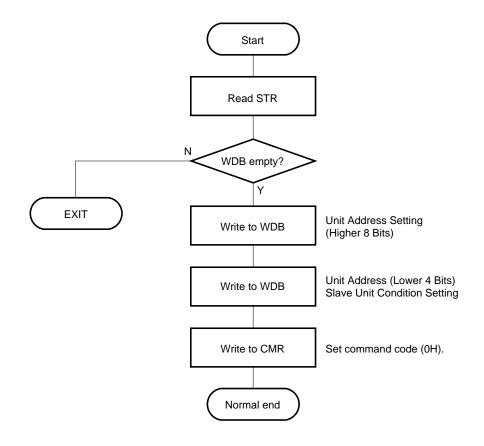

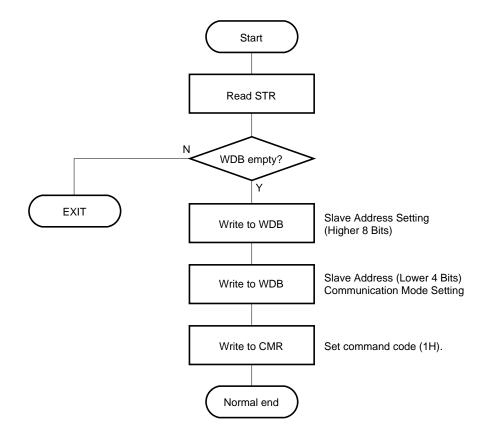

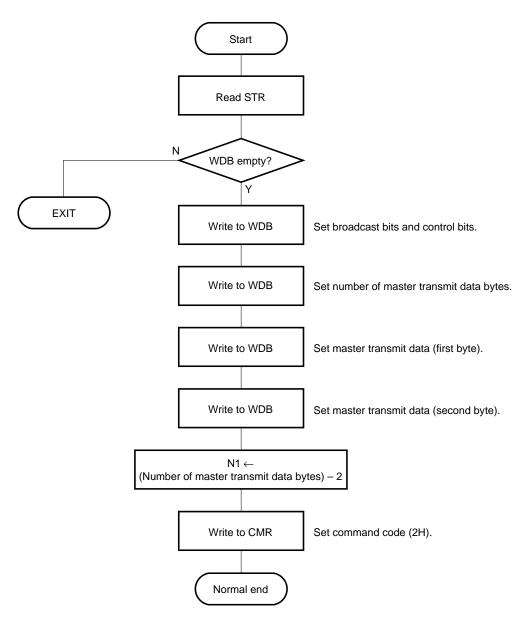

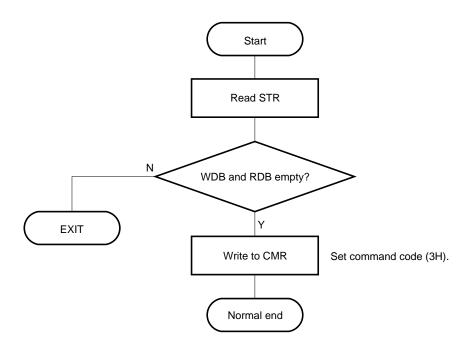

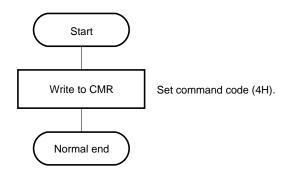

|     |      | 8.3.2    | Communication control command processing routine                        | 51 |

|     |      | 8.3.3    | Master transmission processing routine                                  | 57 |

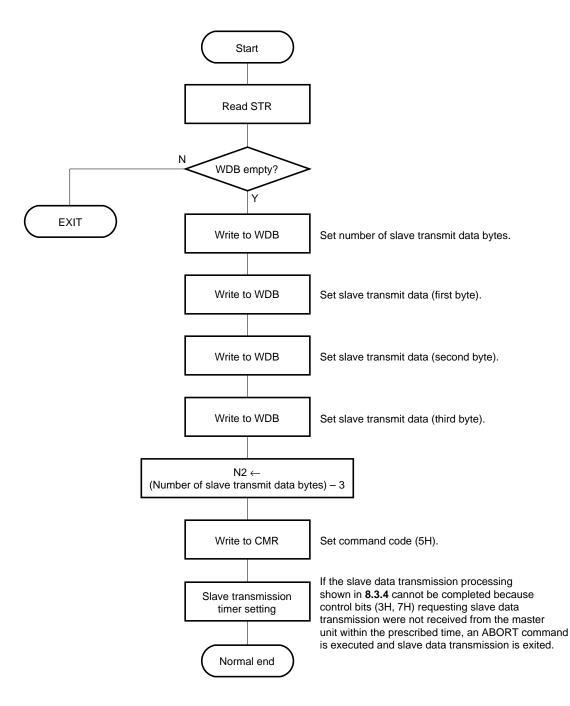

|     |      | 8.3.4    | Slave data transmission processing routine                              | 58 |

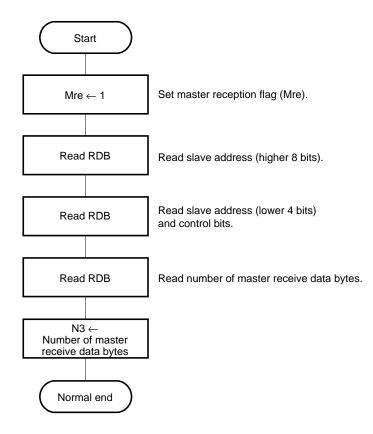

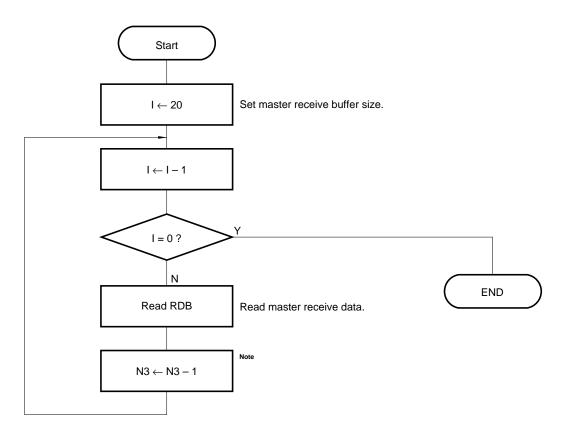

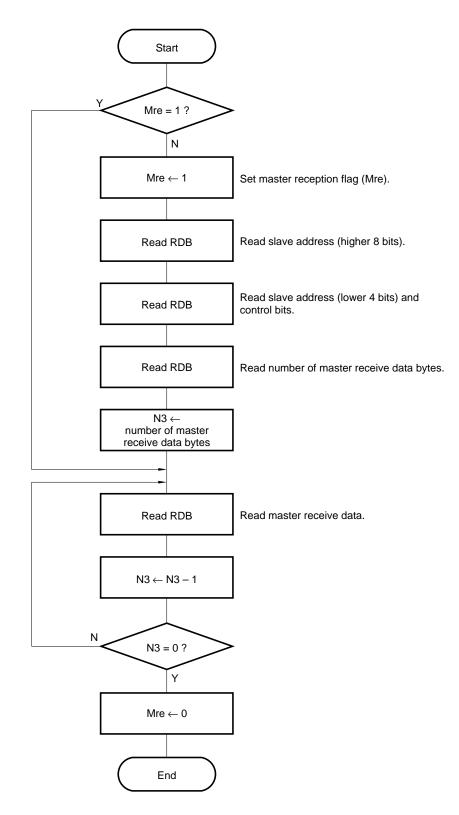

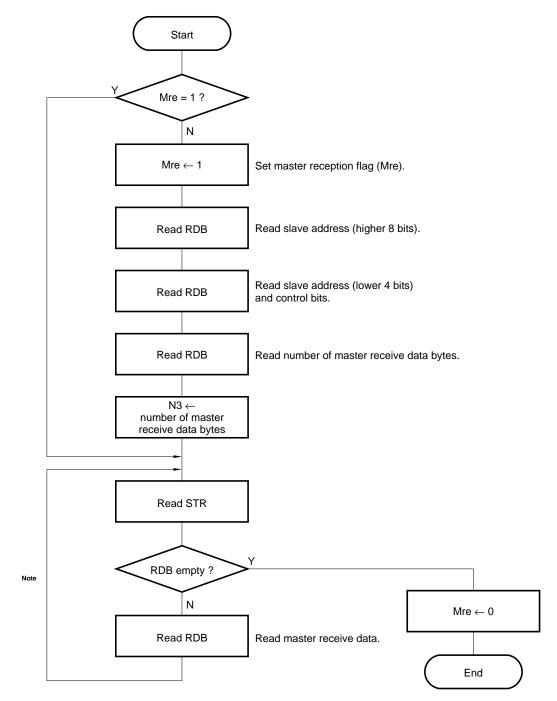

|     |      | 8.3.5    | Master reception processing routine                                     | 59 |

| 9.  | ELE  | CTRICA   | L SPECIFICATIONS                                                        | 63 |

| 10. | PAC  | KAGE D   | RAWINGS                                                                 | 67 |

| 11. | REC  | OMMEN    | DED SOLDERING CONDITIONS                                                | 69 |

| AP  | PEND | IX MA    | JOR DIFFERENCES BETWEEN $\mu$ PD6708 AND $\mu$ PD72042A, $\mu$ PD72042B | 70 |

## 1. PIN FUNCTIONS

### 1.1 List of Pin Functions

| Pin No. | Pin Name     | Input/Output | Function                                                                                                                                                                                                                                                                                                                              | I/O Format  | At Reset                   |  |

|---------|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------|--|

| 1       | SCK          | Input        | Input for serial clock used to interface with microcontroller.                                                                                                                                                                                                                                                                        | CMOS input  | Input                      |  |

| 2       | SI           | Input        | Input for serial data used to interface with microcontroller.                                                                                                                                                                                                                                                                         | CMOS input  | Input                      |  |

| 3       | SO           | Output       | Output for serial data used to interface with microcontroller.                                                                                                                                                                                                                                                                        | CMOS output | High level                 |  |

| 4       | IRQ          | Output       | Output used by interrupt request signals generated by communication and command execution results. Used as operation start request signal to microcontroller. The interrupt request signal is output for 8 $\mu$ s or longer at high level.                                                                                           | CMOS output | Low level                  |  |

| 5       | R/W          | Input        | Input for switching serial interface read/write mode.<br>When high, it is in the read mode. When low, it is in the write mode.<br>When this pin is low and $C/\overline{D}$ pin high, the read and write modes can be switched by commands input from the serial interface.                                                           | CMOS input  | Input                      |  |

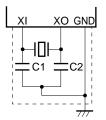

| 6<br>7  | XI<br>XO     |              | Connection pins for system clock resonator.<br>Use a 12- or 12.58-MHz crystal, or ceramic resonator.<br>Frequency precision depends on the communication mode<br>used.<br>Mode 0 : $\pm 1.5$ %<br>Mode 1 : $\pm 1.5$ %<br>Mode 2 : $\pm 0.5$ %                                                                                        |             | (Oscillation<br>continues) |  |

| 8       | GND          |              | Ground                                                                                                                                                                                                                                                                                                                                |             |                            |  |

| 9<br>10 | BUS-<br>BUS+ | Input/output | Input/output for IEBus.                                                                                                                                                                                                                                                                                                               |             | High<br>impedance          |  |

| 11      | AVdd         |              | IEBus driver/receiver analog power supply. Connect to $V_{DD}$ .                                                                                                                                                                                                                                                                      |             |                            |  |

| 12      | C/D          | Input        | Input used to switch between processing data input to the serial interface as commands or data.<br>When set to high, data is processed as commands; when low, data is processed as data.<br>When this pin is high and $R/\overline{W}$ pin low, the read and write modes can be switched by commands input from the serial interface. | CMOS input  | Input                      |  |

| 13      | ĊS           | Input        | Chip select input.<br>When low, serial interface input is enabled.<br>When high, serial clock ( $\overline{SCK}$ ) input is disabled, SO pin<br>becomes high impedance, and the serial clock counter is<br>reset.<br>The status of $\overline{CS}$ pin is not affected by IEBus transmit and<br>receive operations.                   | CMOS input  | Input                      |  |

| 14      | RESET        | Input        | System reset signal input pin.<br>Low input effects a reset.<br>Always input the low signal for 6 $\mu$ s or longer after turning<br>on the power.                                                                                                                                                                                    | CMOS input  | Input                      |  |

| 15      | TEST         | Input        | Always connect this pin to the VDD.                                                                                                                                                                                                                                                                                                   | CMOS input  |                            |  |

| 16      | Vdd          |              | Positive power supply input. Apply a voltage of 5 V $\pm 10$ %.                                                                                                                                                                                                                                                                       |             |                            |  |

$\star$

#### 2. IEBus OPERATION

#### 2.1 Operation Overview

The  $\mu$ PD6708 is an IEBus interface CMOS LSI device.

The IEBus is a bus for a small-scale digital data transfer system designed to transfer data between electronic devices. The  $\mu$ PD6708 is connected to a microcontroller incorporated in electronic equipment with a serial interface (SCK, SO, SI pins). The data and commands required to transfer data with the host controller (microcontroller) are set via this serial interface.

When the host controller transmits data to the  $\mu$ PD6708 via the serial interface, signals are output from the BUS pins (BUS+ and BUS-). Data received from the BUS pins can be read by the host controller via the serial interface.

#### 2.2 IEBus Communication Protocol

An overview of the IEBus is as follows.

- Communication system: Half-duplex asynchronous communication

- Multi-master system All the units connected to the IEBus can transfer data to the other units.

- Broadcast communication function (communication between one unit and multiple units) Group broadcast communication: Broadcast communication with group units General broadcast communication: Broadcast communication with all units.

- Three modes with different transfer speeds selectable.

|        | fx = 12 MHz      | fx = 12.58 MHz   | Maximum Number of Transfer Bytes<br>(bytes/frame) |

|--------|------------------|------------------|---------------------------------------------------|

| Mode 0 | Approx. 3.9 Kbps | Approx. 4.1 Kbps | 16                                                |

| Mode 1 | Approx. 17 Kbps  | Approx. 18 Kbps  | 32                                                |

| Mode 2 | Approx. 26 Kbps  | Approx. 27 Kbps  | 128                                               |

- Access control: CSMA/CD (Carrier Sense Multiple Access with Collision Detection) The priority order for bus occupancy is as follows.

- <1> Broadcast communication takes precedence over ordinary communication (i. e., communication between one unit and another).

- <2> The lowest master address has the highest priority.

- Communication scale

| Number of units: | MAX. 50                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------|

|                  |                                                                                                      |

| Cable length:    | MAX. 150 m (with twisted-pair cable <resistance: 0.1="" <math="">\Omega/m or less&gt;)</resistance:> |

| Load capacity:   | MAX. 8000 pF <between and="" bus+="" bus-="">, fx = 12 MHz</between>                                 |

|                  | MAX. 7100 pF <between and="" bus+="" bus-="">, fx = 12.58 MHz</between>                              |

|                  |                                                                                                      |

Terminating resistor: 120  $\Omega$

7

\*

#### 2.2.1 Bus mastership determination (arbitration)

When a unit connected to the IEBus controls another unit, it performs an operation to occupy the bus. This operation is called arbitration.

Arbitration is to select one unit, and if several units begin to transmit data simultaneously, gives permission to occupy the bus to that one unit.

So that one unit is granted the permission to occupy the bus as a result of the arbitration, the following priority conditions are determined.

**Remark** The units not given permission through arbitration are automatically allowed to get into retransfer mode (number of retransfer times for the  $\mu$ PD6708: 3).

#### (1) Priority according to type of communication

Broadcast communication (between a single and multiple units) takes precedence over ordinary communication (between single units).

#### (2) Priority according to master address

If the communication devices are of the same type, the unit with the lowest master address has the highest priority.

**Example** The master address comprises 12 bits, and unit 000H has the highest priority while unit FFFH has the lowest priority.

#### 2.2.2 Communication modes

The IEBus is provided with three communication modes with different transfer speeds. The transfer speed and maximum number of transfer bytes in a single communication frame in each communication mode are shown in Table 2-1.

| Table 2-1. Transfer Speed and Maximum Number of | f Transfer Bytes in Each Communication Mode |

|-------------------------------------------------|---------------------------------------------|

|-------------------------------------------------|---------------------------------------------|

| Communication Mode | Maximum Number of Transfer Bytes (bytes/frame) | Actual Transfer Speed Note 1 (Kbps) |                       |  |  |  |  |

|--------------------|------------------------------------------------|-------------------------------------|-----------------------|--|--|--|--|

|                    |                                                | fx = 12 MHz Note 2                  | fx = 12.58 MHz Note 2 |  |  |  |  |

| 0                  | 16                                             | Approx. 3.9                         | Approx. 4.1           |  |  |  |  |

| 1                  | 32                                             | Approx. 17                          | Approx. 18            |  |  |  |  |

| 2                  | 128                                            | Approx. 26                          | Approx. 27            |  |  |  |  |

Notes 1. Actual transfer speed when the maximum number of bytes is transferred

**2.** Oscillation frequency when the  $\mu$ PD6708 is used

- Cautions 1. A communication mode is selected for each unit connected to the IEBus before communication is performed. If the communication mode of the master unit is not the same as that of the unit with which the master unit is to communicate (slave unit), communication cannot be performed correctly.

- 2. If the oscillation frequency of one unit is fx = 12 MHz and that of the other unit is fx = 12.58 MHz, communication cannot be performed correctly even if the communication mode is the same. Make sure that the oscillation frequencies of the two units to communicate are the same.

#### 2.2.3 Communication address

With the IEBus, a 12-bit communication address is assigned to each unit. The communication address is made up as follows.

Higher 4 bits: Group number (number which identifies the group to which the unit belongs) Lower 4 bits: Unit number (number which identifies a unit within a group)

#### 2.2.4 Broadcast communication

In ordinary communication, there is only one master unit and one slave unit, and transmission or reception is performed on an one-to-one basis. In broadcast communication, however, there are a number of slave units and the master unit performs transmission with these slave units. Because there are several slave units, no acknowledge signals is returned from the slave units during communication.

Whether broadcast communication or ordinary communication is performed is specified by the broadcast bit (for the broadcast bit, see 2.3 (1) <2> "Broadcast bit").

There are two kinds of broadcast communication, as follows.

#### (1) Group broadcast communication

Broadcast communication is performed to the units in a group whose group numbers are the same as that specified by the higher 4 bits of the communication address.

#### (2) General broadcast communication

Broadcast communication is performed to all units irrespective of their group numbers.

Group broadcast communication or general broadcast communication is identified by the value of a salve address (for the slave address, see **2.3 (3)** "Slave address field").

\*

#### 2.3 Transfer Protocol

The IEBus transfer signal format is shown in Figure 2-1.

Data is transferred as a series of signals called a communication frame. The number of data that can be transferred in one communication frame and the transfer speed differ depending on the communication mode.

#### Figure 2-1. Transfer Signal Format

#### (fx = at 12 MHz)

| Fie  | eld Name   | Header Master<br>Address Field            |                                                     |                   |   | Slave Address   Control Field  <br>Field |   |   |                | Message<br>Length Field |   |                          | Data Field |   |             |   |   |  |             |   |   |

|------|------------|-------------------------------------------|-----------------------------------------------------|-------------------|---|------------------------------------------|---|---|----------------|-------------------------|---|--------------------------|------------|---|-------------|---|---|--|-------------|---|---|

| Numb | er of Bits | 1                                         | 1                                                   | 12                | 1 | 12                                       | 1 | 1 | 4              | 1                       | 1 | 8                        | 1          | 1 | 8           | 1 | 1 |  | 8           | 1 | 1 |

|      |            | Start<br>Bit                              | Broad-<br>cast<br>Bit                               | Master<br>Address | Ρ | Slave<br>Address                         | Ρ | A | Control<br>Bit | Ρ                       | A | Message<br>Length<br>Bit | Ρ          | A | Data<br>Bit | Ρ | A |  | Data<br>Bit | Ρ | A |

| Tran | sfer Time  |                                           |                                                     |                   |   |                                          |   |   |                |                         |   |                          |            |   |             |   |   |  |             |   |   |

|      | Mode 0     |                                           | Approx. 7330 μs         Approx. 1590 × N μs         |                   |   |                                          |   |   |                |                         |   |                          |            |   |             |   |   |  |             |   |   |

|      | Mode 1     | Approx. 2090 μs         Approx. 410 × Nμs |                                                     |                   |   |                                          |   |   |                |                         |   |                          |            |   |             |   |   |  |             |   |   |

|      | Mode 2     |                                           | Approx. 1590 $\mu$ s Approx. 300 $\times$ N $\mu$ s |                   |   |                                          |   |   |                |                         |   |                          |            |   |             |   |   |  |             |   |   |

- P: Parity bit (1 bit)

- A: Acknowledge bit (1 bit) When A = 0: ACK When A = 1: NAK

- N: Number of data bytes

Remark In broadcast communication, the value of the acknowledge bit is ignored.

#### (1) Header

A header comprises a start bit and a broadcast bit, as described below.

#### <1> Start bit

The start bit is a signal which tells the other units that data transmission will start.

The unit which is about to start transmitting data will output the low signal (the start bit) for a specified time, and then outputs the broadcast bit.

If another unit is already outputting a start bit before one unit outputs a start bit, the unit will not output the start bit. It will wait until the another unit completely outputs the start bit, and then outputs the broadcast bit.

The units other than the one that has started transmission detect this start bit and enters the reception state.

#### <2> Broadcast bit

The broadcast bit distinguishes between broadcast communication and ordinary communication.

When this bit is '0', it indicates broadcast communication; when it is '1', it indicates ordinary communication. There are two types of broadcast communication: group broadcast and general broadcast. These types are identified by the value of the slave address (for the slave address, see (3) "Slave address field").

In broadcast communication, there are a number of slave units. Therefore, the acknowledge bit is not returned in the fields described in (2) below and onward.

If two or more units start to transmit a communication frame simultaneously, broadcast communication takes precedence over ordinary communication, and wins in the arbitration.

#### (2) Master address field

The master address field is used to transmit the unit address of the master unit (master address) to the other units. The master address field consists of master address bits and a parity bit.

The master address comprises 12 bits and is output from the MSB.

If two or more units start transmitting the broadcast bit of the same value simultaneously, the arbitration decision is made by the master address field.

The master address field compares the data the master has output with the data on the bus each time the master transmits 1 bit of data. If the master address output by the master unit is different from the data on the bus, the master unit assumes that it has lost in arbitration, stops transmission, and enters the reception state.

Because the IEBus has a wired-AND configuration, the unit having the lowest master address of the units participating in the arbitration (arbitration masters) wins in the arbitration. Ultimately, only one unit remains in the transmission state as the master unit after outputting a 12-bit master address.

This master unit then outputs a parity bit <sup>Note</sup>, makes the other units confirm the master address, and then outputs the slave address field.

Note Even parity is used. When the number of the bits that are '1' in the master address is odd, the parity bit is '1'.

#### (3) Slave address field

The slave address field is used to transmit the address (slave address) of a unit (slave unit) with which the master wishes to communicate.

The slave address field consists of slave address bits, a parity bit, and an acknowledge bit.

The slave address comprises 12 bits and is output from the MSB. After the 12-bit slave address is transmitted, the parity bit is output to prevent the slave address from being received incorrectly. Next, the master unit looks for the acknowledge signal (bit) from the slave unit to confirm that the slave unit exists on the bus. When the master unit detects the acknowledge signal, it starts outputting the control field. In the case of broadcast communication, however, the master unit outputs the control field without waiting for the acknowledge bit.

A slave unit outputs the acknowledge signal if it has detected that its slave address coincides with that selected by the master and that the parities of both the master and slave addresses are even. If the parity is odd, the slave unit assumes that the master or slave address has not been correctly received, and does not output the acknowledge signal. In this case, the master unit enters the standby (monitor) state and communication ceases.

In the case of broadcast communication, the slave address is used to distinguish between group broadcast and general broadcast as follows:

Slave address = FFFH: General broadcast communication Slave address ≠ FFFH: Group broadcast communication

**Remark** In the case of group broadcast communication, the group number is the value of higher 4 bits of the slave address.

#### (4) Control field

The control field indicates the type of data and the transfer direction of the subsequent data field.

The control field consists of 4 control bits, a parity bit, and an acknowledge bit.

The control bits are output from the MSB.

A parity bit is output after the control bits. When the parity is even and the slave can execute the function requested by the master unit, the slave unit outputs an acknowledge signal, and then outputs the next message length field. If the slave unit cannot execute the function requested by the master unit even if the parity is even, or if the parity is odd, the slave unit does not output the acknowledge signal but returns to the standby (monitor) state.

After the master unit has confirmed the acknowledge signal, it starts outputting the next message length field.

If the master unit is cannot confirm the acknowledge signal, it enters the standby state and stops communication. In the case of broadcast communication, however, the master unit starts outputting the message length field without confirming the acknowledge signal.

For the functions of the control bits, see Table 2-3.

#### (5) Message length field

The message length field is used to specify the number of communication data bytes.

The message length field comprises 8 message length bits, a parity bit and, an acknowledge bit.

The message length bits are output from the MSB. The message length bits indicate the number of communication data bytes as shown in Table 2-2.

| Message Length Bits (hex) | Number of Transmission Data Bytes |

|---------------------------|-----------------------------------|

| 01H                       | 1 byte                            |

| 02H                       | 2 bytes                           |

| :                         | :                                 |

| :                         | :                                 |

| FFH                       | 255 bytes                         |

| 00H                       | 256 bytes                         |

#### Table 2-2. Meaning of Message Length Bits

**Remark** In the communication mode, if the number of bytes exceeding the maximum number of transfer bytes per frame is set, two or more frames are communicated. In this case, the message length bits indicate the number of remaining communication data bytes during the second communication and onward.

The operation of this field differs depending on whether the master transmits (bit 3 of control bits is 1) or receives (bit 3 of control bits is 0) data.

#### <1> When master transmits data

The message length bits and parity bit are output by the master unit. The slave unit outputs the acknowledge signal and then the next data field if it detects that the parity is even. The slave unit does not output the acknowledge signal in the case of broadcast communication.

If the parity is odd, the slave unit assumes that the message length bits have not been received correctly, and returns to the standby (monitor) state without outputting the acknowledge signal. In this case, the master unit also returns to the standby state, and communication ceases.

#### <2> When master receives data

The message length bits and parity bit are output by the slave unit. The master unit outputs the acknowledge signal **#** if it detects that the parity bit is even.

If the parity is odd, the master unit assumes that the message length bits have not been received correctly, and returns to the standby state without outputting the acknowledge signal. In this case, the slave unit also returns to the standby state, and communication ceases.

#### (6) Data field

The data field is used to transmit/receive data to/from the slave units.

The master unit uses the data field to transmit data to and receive data from the slave units.

The data field consists of 8 data bits, a parity bit, and an acknowledge bit.

The data bits are output from the MSB.

Following the data bits, the parity bit and acknowledge bit are output from the master unit and the slave unit, respectively.

Broadcast communication is performed when only the master unit transmits data. At this time, the acknowledge signal is ignored.

The operation differs depending on whether the master performs transmission or reception, as follows.

#### <1> When master transmits data

When the master unit writes data to the slave unit, the master unit transmits data bits and a parity bit to the slave unit. The slave unit receives the data bits and parity bit. If the parity is even and the receive buffer is empty, the slave unit outputs the acknowledge signal. If the parity is odd and the receive buffer is not empty, the slave unit denies acknowledgment of the corresponding data and does not output the acknowledge signal.

If no acknowledge signal is output from the slave unit, the master unit transmits the same data again. The master unit continues this operation until it detects the acknowledge signal from the slave unit or the data reaches the maximum number of transfer bytes.

If the parity is even and the acknowledge signal has been output from the slave unit, and if the master unit has more data to transmit and the maximum number of transfer bytes is not exceeded, the master unit will transmit the next data.

In the case of broadcast communication, the slave unit does not output the acknowledge signal, and the master unit transfers data on a byte-by-byte basis.

#### <2> When master receives data

When the master unit reads data from the slave unit, the master unit outputs synchronization signals corresponding to all the read bits.

The slave unit outputs the contents of the data and parity bits onto the bus in accordance with the synchronization signals from the master unit.

The master unit reads the data and parity bit output by the slave unit, and checks the parity.

If the parity is odd or the receive buffer is not empty, the master unit denies acknowledgement of that data and does not output the acknowledge signal. If the data is within the maximum number of transfer bytes that can be transmitted in one frame, the master unit repeatedly reads the same data.

If the parity is even and the receive buffer is empty, the master unit acknowledges the data and transmits back the acknowledge signal. If the data is within the maximum number of bytes that can be transmitted in one frame, the master unit reads the next data.

# NEC

#### (7) Parity bits

Parity bits are used to check that there is no error in the transfer data.

A parity bit is added to the master address bits, slave address bits, control bits, message length bits, and data bits. Even parity is used. If the number of the bits that are '1' bits in data is odd, the parity bit is '1', and if the number of the bits that are '1' bits is even, the parity bit is '0'.

#### (8) Acknowledge bits

In ordinary communication (between two units), an acknowledge bit is added to the following places to confirm that data has been acknowledged correctly.

- At the end of the slave address field.

- At the end of the control field.

- At the end of the message length field.

- At the end of a data field.

The definition of the acknowledge bit is as follows.

- '0': Indicates that transfer data has been acknowledged (ACK).

- '1': Indicates that transfer data has not been acknowledged (NAK).

Note that the value of the acknowledge bit is ignored in broadcast communication.

#### <1> Acknowledge bit at the end of the slave field

When any of the following conditions is met, the acknowledge bit at the end of the slave field is NAK, and communication is discontinued.

- If the parity of the master address bits or slave address bits is incorrect.

- If a timing error (error in bit format) occurs.

- If the slave unit does not exist.

#### <2> Acknowledge bit at the end of the control field

When any of the following conditions is met, the acknowledge bit at the end of the control field is NAK, and communication is discontinued.

- If the parity of the control bits is incorrect.

- If bit 3 of the control bits is '1' (write operation) when the slave receive buffer Note is not empty.

- If the control bits indicate read operation (3H or 7H) when the slave transmit buffer Note is empty.

- If 3H, 6H, 7H, AH, BH, EH, or FH of control bits is requested from a unit other than the unit which set the lock when a lock has been set.

- If the control bits indicate lock address read (4H) when a lock has not been set.

- If a timing error occurs.

- If the control bits are undefined.

Note See 2.4 (1) "Reading slave status (SSR) (control bit: 0H, 6H)".

#### <3> Acknowledge bit at the end of a message length field

When either of the following conditions is met, the acknowledge bit at the end of the message length field is NAK, and communication is discontinued.

- If the parity of the message length bits is incorrect.

- If a timing error occurs.

#### <4> Acknowledge bit at the end of a data field

When any of the following conditions is met, the acknowledge bit at the end of a data field is NAK, and communication is discontinued.

- If the parity of the data bits is incorrect Note.

- If a timing error occurred in or after the previous acknowledge bit transmission.

- If the receive buffer is full and cannot accept any more data Note.

- **Note** In this case, if the number of transfer bytes is within the maximum number of bytes which can be transmitted, the transmitting side re-executes transmission of that data field.

★

#### 2.4 Transfer Data (Contents of Data Field)

The contents of the data field are data specified by the control bits.

| $\square$ | Bit 3 Note 1 | Bit 2 | Bit 1 | Bit 0 | Function Note 2                      |

|-----------|--------------|-------|-------|-------|--------------------------------------|

| ОH        | 0            | 0     | 0     | 0     | Reads slave status (SSR)             |

| 1H        | 0            | 0     | 0     | 1     | Undefined                            |

| 2H        | 0            | 0     | 1     | 0     | Undefined                            |

| ЗH        | 0            | 0     | 1     | 1     | Reads and locks data                 |

| 4H        | 0            | 1     | 0     | 0     | Reads lock address (lower 8 bits)    |

| 5H        | 0            | 1     | 0     | 1     | Reads lock address (higher 4 bits)   |

| 6H        | 0            | 1     | 1     | 0     | Reads and unlocks slave status (SSR) |

| 7H        | 0            | 1     | 1     | 1     | Reads data                           |

| 8H        | 1            | 0     | 0     | 0     | Undefined                            |

| 9H        | 1            | 0     | 0     | 1     | Undefined                            |

| AH        | 1            | 0     | 1     | 0     | Writes and locks command             |

| вн        | 1            | 0     | 1     | 1     | Writes and locks data                |

| СН        | 1            | 1     | 0     | 0     | Undefined                            |

| DH        | 1            | 1     | 0     | 1     | Undefined                            |

| EH        | 1            | 1     | 1     | 0     | Writes command                       |

| FH        | 1            | 1     | 1     | 1     | Writes data                          |

#### Table 2-3. Functions of Control Bits

**Notes 1.** Depending on the value of bit 3 (MSB), the transfer direction of the message length bits of the subsequent message field and data field differs.

When bit 3 is "1", data are transferred from the master unit to the slave unit.

When bit 3 is "1", data are transferred from the slave unit to the master unit.

3H, 6H, AH, and BH are control bits that specify locking or unlocking. If any of undefined values 1H, 2H, 8H, 9H, CH, or DH is transmitted, no acknowledge bit is returned.

A unit locked by the master unit rejects acknowledging the control bits and does not output the acknowledge bit if the control bits received from the master unit which requested locking is in any other state than that shown in Table 2-4.

| Table 2-4. | Control Field Correspondin | g to Locked Slave Unit |

|------------|----------------------------|------------------------|

|------------|----------------------------|------------------------|

|    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Function                           |

|----|-------|-------|-------|-------|------------------------------------|

| 0H | 0     | 0     | 0     | 0     | Reads slave status                 |

| 4H | 0     | 1     | 0     | 0     | Reads lock address (lower 8 bits)  |

| 5H | 0     | 1     | 0     | 1     | Reads lock address (higher 4 bits) |

\*

#### (1) Reading slave status (SSR) (control bit: 0H, 6H)

The master unit can learn the reason why the slave unit has not returned the acknowledge bit (ACK) by reading the slave status.

The slave status is determined by the results of the last communication performed by the slave unit.

All the slave units can provide slave status information.

The meanings of the slave status are shown in Table 2-5.

#### Figure 2-2. Bit Configuration of Slave Status (SSR)

| MSB   |       |       |       |       |       |       | LSB   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Bit          | Value | Meaning                    |                                     |  |  |

|--------------|-------|----------------------------|-------------------------------------|--|--|

| Bit 0 Note 1 | 0     | Slave transmit buffer em   | pty                                 |  |  |

|              | 1     | Slave transmit buffer is r | not empty.                          |  |  |

| Bit 1 Note 2 | 0     | Slave receive buffer emp   | oty                                 |  |  |

|              | 1     | Slave receive buffer is n  | ot empty.                           |  |  |

| Bit 2        | 0     | Unit is not locked.        |                                     |  |  |

|              | 1     | Unit is locked.            |                                     |  |  |

| Bit 3        | 0     | Fixed to '0'               |                                     |  |  |

| Bit 4 Note 3 | 0     | Slave transmission ends    |                                     |  |  |

|              | 1     | Slave transmission enabled |                                     |  |  |

| Bit 5        | 0     | Fixed to '0'               |                                     |  |  |

| Bit 7        | 00    | Mode 0                     | Indicates the highest mode the unit |  |  |

| Bit 6        | 01    | Mode 1                     | supports Note 4.                    |  |  |

|              | 10    | Mode 2                     |                                     |  |  |

|              | 11    | For future expansion       |                                     |  |  |

#### Table 2-5. Meanings of Slave Status

- Notes 1. The slave transmit buffer is the buffer accessed during data read processing (control bits: 3H, 7H). With the μPD6708, this buffer corresponds to the write data buffer (WDB) when the SETSD command is valid (see 5.2.6 "SETSD command").

- 2. The slave receive buffer is the buffer accessed during data write processing (control bits: 8H, AH, BH, EH, FH). With the  $\mu$ PD6708, this buffer corresponds to the read data buffer (RDB).

- 3. The value of bit 4 can be selected by INIT command (see 5.2.1 "INIT command").

- 4. Because the  $\mu$ PD6708 can support mode 2, bits 7 and 6 are fixed at '10'.

#### (2) Transferring data command (control bit: read (3H, 7H), write (AH, BH, EH, FH))

During data read (3H, 7H), the data in the data buffer of the slave unit are read to the master unit. During data write (BH, FH) or during command write (AH, EH), the data the slave unit has received are processed according to the operation convention.

#### **Remarks** 1. The user can voluntarily select data and command as his system requires.

2. Control bits 3H, AH, and BH may be locked depending on the communication condition and status.

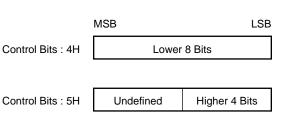

#### (3) Reading lock address (control bits: 4H, 5H)

When the lock address is read processing (4H, 5H), the address (12 bits) of the master unit that has issued the lock instruction is read in 1-byte units, as shown below.

#### Figure 2-3. Lock Address Configuration

#### (4) Locking and unlocking (locking (3H, AH, BH), unlocking (6H))

The lock function is used to transfer a message over two or more frames. A locked unit receives data only from the unit that has locked the unit. Locking and unlocking are performed as described below.

#### <1> Locking

After the transmission/reception of the acknowledge bit '0' of the message length field by the control bits (3H, AH, BH) which specify the lock has ended, if the communication frame is completed without completing the transmission or reception of the number of data bytes specified by the message length bits, the slave unit is locked by the master unit. At this time, the bit (bit 2) relating to the locking of the byte which indicates the slave status is set to '1'.

#### <2> Unlocking

After completion of transmission or reception of data in one frame by the number of data bytes specified by the message length bits with control bits (3H, AH, or BH) specifying locking or control bits (6H) specifying unlocking, the slave unit is unlocked by the master unit. At this time, the bit (bit 2) relating to the locking of the byte which indicates the slave status is reset to '0'.

Locking and unlocking are not performed in the case of broadcast communication.

Caution To unlock the unit specified to be unlocked by the unit itself, the INIT command (see 5.2.1 "INIT command") must be executed with the  $\mu$ PD6708 (Whether a unit is locked or not can be checked by using the GETSA command (see 5.2.7 "GETSA command").

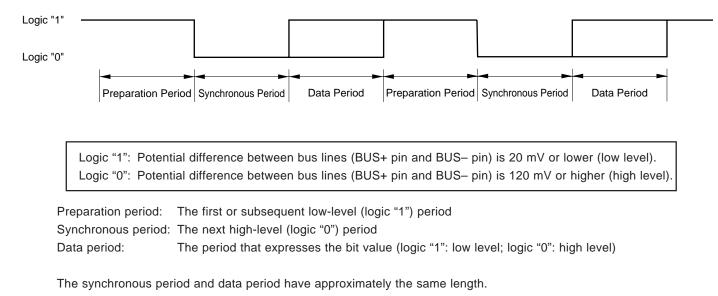

#### 2.5 Bit Format

The IEBus communication frame bit format (concept) is shown in Figure 2-4.

Figure 2-4. IEBus Bit Format (Concept)

The IEBus uses bit-by-bit synchronization. The specifications for the total bit time and the periods allocated to the bits depend on the type of transfer bit, and on whether the unit is the master unit or the slave unit.

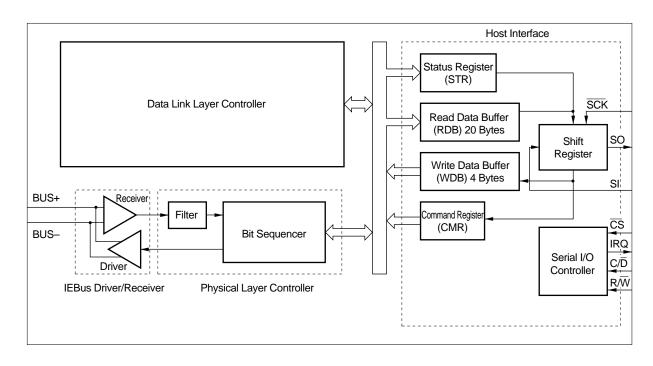

#### 3. INTERNAL CONFIGURATION

The  $\mu$ PD6708 is composed of the following four blocks.

- (1) Data link layer controller

- (2) Physical layer controller

- (3) IEBus driver/receiver

- (4) Host interface

#### 3.1 Data Link Layer Controller

The data link layer controller performs processing of the IEBus protocol data link layer (frame composition and resolution, communication error detection, etc.), execution of communication control commands set by the host controller, and generate a return code that informs the host controller of the communication status.

#### 3.2 Physical Layer Controller

The physical controller performs generation and resolution of bit timing and also converts the signals between the bus lines through the driver/receiver.

#### 3.3 IEBus Driver/Receiver

The driver/receiver performs conversion between the logic signals within the  $\mu$ PD6708 and the IEBus signals. The IEBus signals and their relationship to the logic statuses are shown in Table 3-1.

| Logical Status | IEBus Signals                |

|----------------|------------------------------|

| 0              | $(BUS+) - (BUS-) \ge 120 mV$ |

| 1              | (BUS+) – (BUS–) ≤ 20mV       |

#### Table 3-1. Relationship between IEBus Signals and Logical Statuses

#### 3.4 Host Interface

The host Interface is a block which controls the transmission and reception of data to and from the host controller. It accepts communication control commands, passes on return codes, and forwards transmit data.

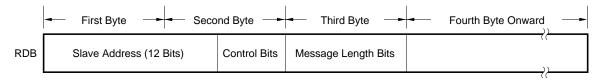

The forwarding of transmit data takes place through the FIFO buffers, 4 bytes of write data buffer (WDB) and 20 bytes of read data buffer (RDB). It also absorbs the differences between IEBus transmission speed and the transmission speed on the serial interface between the  $\mu$ PD6708 and the host controller.

#### 4. INTERFACING WITH HOST CONTROLLER

This chapter will explain the interfacing that occurs between the  $\mu$ PD6708 and the host controller.

#### 4.1 Accessible Buffers and Registers from Host Controller

The host controller, which controls the  $\mu$ PD6708, can access the write data (WDB), the read data buffer (RDB), the command register (CMR), and the status register (STR) within the  $\mu$ PD6708.

#### 4.1.1 Write data buffer (WDB)

WDB is a 4-byte FIFO buffer in which the host controller transmit data and the parameters of the communication control commands are written.

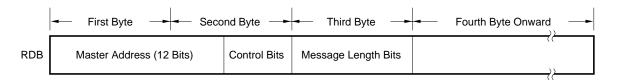

#### 4.1.2 Read data buffer (RDB)

RDB is a 20-byte FIFO buffer which stores the receive data acknowledged by the data link layer controller in the  $\mu$ PD6708. The host controller reads the  $\mu$ PD6708 receive data from RDB.

#### 4.1.3 Command register (CMR)

CMR is an 8-bit register used to write control commands for the  $\mu$ PD6708.

As shown in Table 4-1, the host controller sets the reset mode and the host interface mode in higher 4 bits and sets the communication control command code in lower 4 bits.

| Bit               | Value | Meaning                                                             |  |  |

|-------------------|-------|---------------------------------------------------------------------|--|--|

| Bit 7             | 1     | Entering the reset mode                                             |  |  |

|                   | 0     | Exiting the reset mode                                              |  |  |

| Bit 6             | 1     | Data of lower 4 bits of CMR is valid.                               |  |  |

|                   | 0     | Data of lower 4 bits of CMR is not valid.                           |  |  |

| Bit 5             | 00    | Change of mode through pin control Switches the host interface mode |  |  |

| Bit 4             | 01    | Data write mode                                                     |  |  |

|                   | 10    | Data read mode                                                      |  |  |

|                   | 11    | Status read mode                                                    |  |  |

| Bit 3 to<br>Bit 0 |       | Set the communication control command codes                         |  |  |

#### Table 4-1. Contents of Command Register

#### 4.1.4 Status register (STR)

STR is an 8-bit register used to determine the status of the  $\mu$ PD6708.

The statuses of WDB and RDB and the status of interrupts can be read from higher 4 bits. The return code, which indicates the result of the communication, can be read from lower 4 bits.

| Bit               | Value | Meaning                 | Description                                                                   |  |

|-------------------|-------|-------------------------|-------------------------------------------------------------------------------|--|

| Bit 7             | 1     | WDB is full             | Indicates whether data can be written to WDB                                  |  |

|                   | 0     | WDB is not full         |                                                                               |  |

| Bit 6             | 1     | RDB is empty            | Indicates whether data can be read from RDB                                   |  |

|                   | 0     | RDB is not empty        |                                                                               |  |

| Bit 5             | 1     | WDB is empty            | Indicates whether data is in WDB                                              |  |

|                   | 0     | WDB is not empty        |                                                                               |  |

| Bit 4             | 1     | Interrupt requested     | Indicates whether interrupt servicing is being requested (Bit 4 of the status |  |

|                   | 0     | Interrupt not requested | register is reset by STR by the host controller)                              |  |

| Bit 3 to<br>Bit 0 |       | Return code             | Return code will be read                                                      |  |

#### Table 4-2. Contents of Status Register

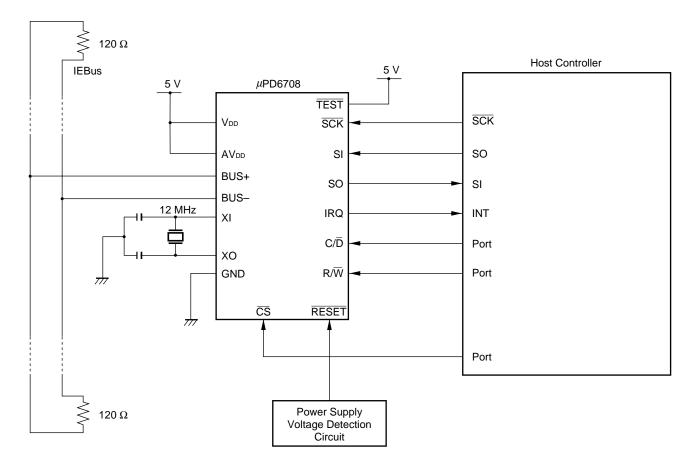

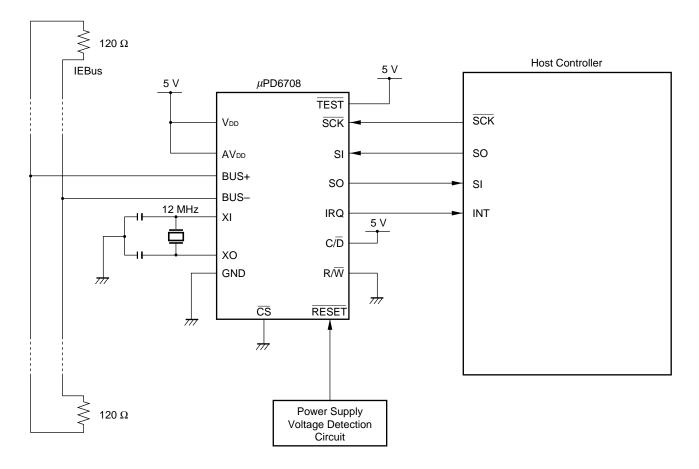

#### 4.2 Host Interface Modes

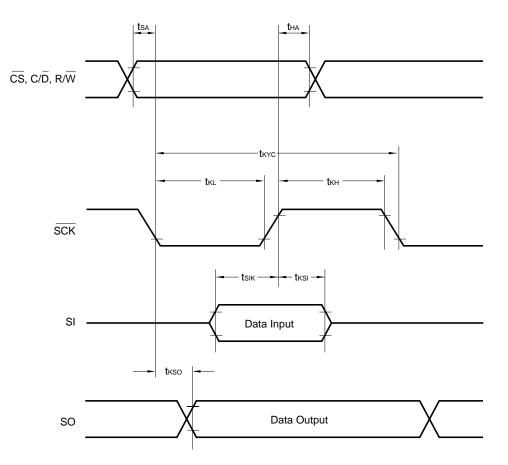

The host controller can access WDB, RDB, CMR, and STR within the  $\mu$ PD6708 via the serial interface (SCK, SI, SO). There are four modes for accessing the serial interface, as shown in the Table 4-3.

There are two method for switching among these four host interface modes: by using  $C/\overline{D}$  pin and  $R/\overline{W}$  pin, and by writing data to CMR (software control).

| Table | 4-3. | Host | Interface | Mode |

|-------|------|------|-----------|------|

|-------|------|------|-----------|------|

| Mode               | Operation                                                                                                                                                                                                |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data write mode    | Data input to SI pin is written to WDB from MSB at the rising edge of the serial clock input to $\overline{SCK}$ pin. Data setting is completed at the eighth serial clock cycle.                        |  |

| Data read mode     | RDB data is output from MSB to SO pin at the falling edge of the serial clock input to $\overline{SCK}$ pin. A data read is completed by inputting eight serial clock cycles. Data at SI pin is ignored. |  |

| Command write mode | Data input to SI pin is written to CMR from MSB at rising edge of the serial clock input to SCK pin. Data setting is completed at the eight serial clock cycle.                                          |  |

| Status read mode   | STR data is output from MSB to SO pin at the falling edge of the serial clock input to $\overline{SCK}$ pin. A data read is completed by inputting eight serial clock cycles. Data at SI pin is ignored. |  |

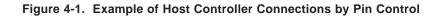

#### 4.2.1 Switching through pin control

With bits 5 and 4 of CMR both '0', the host interface mode can be switched by setting the  $C/\overline{D}$  pin and  $R/\overline{W}$  pin to the values shown in Table 4-4.

| C/D | R/W | Host Interface Mode |  |

|-----|-----|---------------------|--|

| 0   | 0   | Data write mode     |  |

| 0   | 1   | Data read mode      |  |

| 1   | 0   | Command write mode  |  |

| 1   | 1   | Status read mode    |  |

Table 4-4. Switching Host Interface Mode by Pin Control

Caution If the power supply voltage moves out of the 5 V  $\pm$ 5 % range, the RESET pin must be driven low for 6  $\mu$ s or more in order to reset the  $\mu$ PD6708.

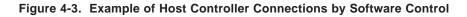

#### 4.2.2 Switching through software control

With the C/ $\overline{D}$  pin at the high level and the R/ $\overline{W}$  pin at the low level, the host interface mode can be switched from the host controller by setting bits 5 and 4 of CMR to the values shown in Table 4-5.

| Bit 5 | Bit 4 | Host Interface Mode           |

|-------|-------|-------------------------------|

| 0     | 0     | Mode switching by pin control |

| 0     | 1     | Data write mode               |

| 1     | 0     | Data read mode                |

| 1     | 1     | Status read mode              |

#### Table 4-5. Switching Host Interface Mode by Software Control

After one byte of data has been forwarded, the host interface mode will become the command write mode, which is controlled by the  $C/\overline{D}$  and  $R/\overline{W}$  pins.

**Remark** Connect  $C/\overline{D}$  and  $R/\overline{W}$  pins to VDD and GND, respectively.

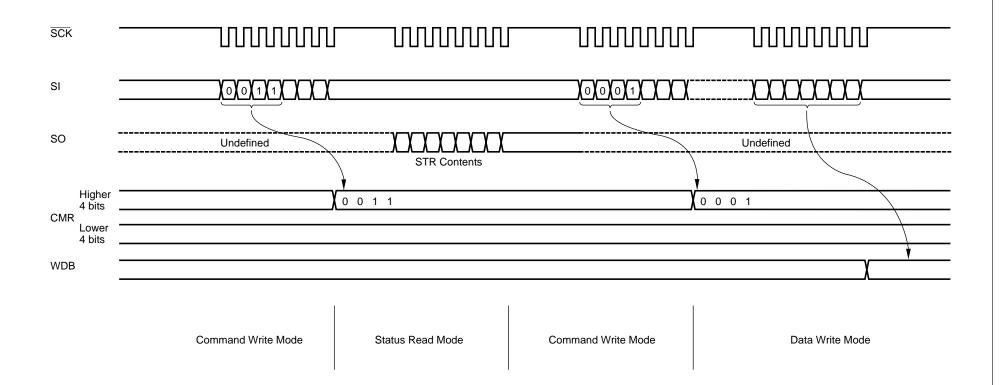

#### 4.3 Reset Mode

When the  $\overrightarrow{\text{RESET}}$  pin is driven low, the  $\mu$ PD6708 enters the reset mode. To release the reset mode, the  $\overrightarrow{\text{RESET}}$  pin must be driven high and a reset release command input.

There are two methods of resetting the  $\mu$ PD6708, as follows.

#### (1) Resetting with $\overline{\text{RESET}}$ pin

If the  $\overline{\text{RESET}}$  pin is driven low, the  $\mu$ PD6708 will enter the reset mode. To exit the reset mode, drive the  $\overline{\text{RESET}}$  pin high and set bit 7 of CMR to '0'.

#### (2) Resetting by software

If bit 7 of CMR is set to '1' with the  $\overrightarrow{\text{RESET}}$  pin fixed high, the  $\mu$ PD6708 will enter the reset mode. To exit the reset mode, set bit 7 to '0'.

When powering on, the  $\overrightarrow{\text{RESET}}$  pin must be driven low to execute a reset. The  $\mu$ PD6708 will be in the following condition directly after leaving the reset mode.

<1> IEBus slave status is intialized.

| Bit   | Value | Meaning                                     |

|-------|-------|---------------------------------------------|

| Bit 7 | 1     | Up to mode 2 is supported                   |

| Bit 6 | 0     |                                             |

| Bit 5 | 0     | Always '0'                                  |

| Bit 4 | 0     | The slave transmission section has stopped. |

| Bit 3 | 0     | Always '0'                                  |

| Bit 2 | 0     | Unit is not locked.                         |

| Bit 1 | 0     | Slave receive buffer is empty.              |

| Bit 0 | 0     | Slave transmit buffer is empty.             |

#### Table 4-6. Slave Status Values after Leaving Reset Mode

<2> WDB and RDB are empty.

#### <3> Reception is disabled.

Slave reception and broadcast reception are not acknowledged.

#### Figure 4-5. Example of RESET Control on Powering on

29

#### 5. COMMUNICATION CONTROL COMMANDS

The operation conditions of the  $\mu$ PD6708 can be controlled by giving it a command from the host controller. After a communication using the appropriate procedure (see **8.3.2** "**Communication control command processing routine**"), it is executed in a period in which communication is not being performed (standby state).

#### 5.1 Overview of Communication Control Commands

| Command Name |                     | Description                                                          |  |  |

|--------------|---------------------|----------------------------------------------------------------------|--|--|

| INIT         | (Initialize)        | Sets local address and initializes.                                  |  |  |

| SETSA        | (Set slave address) | Sets the unit to communicate with.                                   |  |  |

| MREQ1        | (Master request 1)  | Communicates as a master unit.                                       |  |  |

| MREQ2        | (Master request 2)  | Continues in previous condition as the master unit and communicates. |  |  |

| ABORT        | (Abort)             | Aborts communications.                                               |  |  |

| SETSD        | (Set slave data)    | Sets data for slave transmission.                                    |  |  |

| GETSTA       | (Get status)        | Reads communication status.                                          |  |  |

| SETREV       | (Set receive)       | Sets reception disabled state/enabled state.                         |  |  |

#### Table 5-1. Overview of Communication Control Commands

#### (1) Write command

The command codes and command parameters for the write commands are shown in Table 5-2.

Table 5-2. Command Codes and Command Parameters of Write Commands

| Commend Name                       | Command Code | Command Parameters (WDB) |                           |             |                                        |                                                      |                                            |

|------------------------------------|--------------|--------------------------|---------------------------|-------------|----------------------------------------|------------------------------------------------------|--------------------------------------------|

| Command Name (Lower 4 Bits of CMR) |              | Firs                     | st Byte                   | Second Byte |                                        | Third Byte                                           | Fourth Byte                                |

| INIT                               | 0000         |                          | Unit address              | ;           | Condition<br>setting<br>code           |                                                      |                                            |

| SETSA                              | 0001         |                          | Slave addres              | s           | 0000                                   |                                                      |                                            |

| MREQ1                              | 0010         | Broad-<br>cast bits      | Control bits              |             | of master<br>Ita bytes <sup>Note</sup> | Master transmit<br>data (first byte) <sup>Note</sup> | Master transmit<br>data (second byte) Note |

| MREQ2                              | 0011         |                          |                           |             |                                        |                                                      |                                            |

| ABORT                              | 0100         |                          |                           |             |                                        |                                                      |                                            |

| SETSD                              | 0101         |                          | er of slave<br>data bytes |             | transmit<br>irst byte)                 | Slave transmit<br>data (second byte)                 | Slave transmit<br>data (third byte)        |

| SETREV                             | 0111         | · ·                      | tion status<br>code       |             |                                        |                                                      |                                            |

|                                    | MSB LSB      | MSB                      | LSB                       | MSB         | LSB                                    | MSB LSB                                              | MSB LSB                                    |

**Note** Only set when transmitting.

Caution Note that even if the host controller makes a mistake in setting the number of command parameter bytes, an error message will not be returned by the  $\mu$ PD6708, and command processing will be performed as though it were a correctly set command.

#### (2) Read command

The command code of the read command is shown in Table 5-3.

| Command Name | Command Code<br>(Lower 4 Bits of | Data Placed in RDB after Command Execution |            |                          |  |

|--------------|----------------------------------|--------------------------------------------|------------|--------------------------|--|

| Command Name | CMR)                             | Firs                                       | t Byte     | Second Byte              |  |

| GETSTA       | 0110                             | Lock status                                | Address of | of locked unit (12 bits) |  |

|              | MSB LSB                          | MSB LSB                                    | MSB        | LSB                      |  |

Table 5-3. Command Code of Read Command

**Remark** With a read command, the command execution result is placed in RDB, and therefore it is performed in the reception disabled state.

#### 5.2 Communication Control Command Functions

#### 5.2.1 INIT command (command code: 0000)

#### (1) Functions

#### <1> Unit address setting

This command sets the unit address (12 bits), The unit address will be used as the master address when a unit is communicating as the master unit, and as the slave address when a unit is communicating as the slave.

#### <2> Condition setting

- The status of bit 4 of IEBus slave status is set.

Slave transmission block operation enabled, stopped (bit 4) (Setting of use/non-use of the function that transmits data to the master unit)

- The communication mode to be used is set.

#### Table 5-4. Condition Setting Method

| Condition Setting Code |    | Condition Setting Contents           |  |  |

|------------------------|----|--------------------------------------|--|--|

| Bits 3 and 2           | 00 | Communication performed in mode 0    |  |  |

|                        | 01 | Communication performed in mode 1.   |  |  |

|                        | 10 | Communication performed in mode 2.   |  |  |

|                        | 11 | Undefined                            |  |  |

| Bit 1                  | 0  | Fixed at '0'                         |  |  |

| Bit 0                  | 0  | Slave transmission block stopped     |  |  |

| 1                      |    | Slave transmission block operational |  |  |

The local-station address and condition setting contents set by INIT command retain their set values unless power is turned off or reset mode is entered (see **4.3** "**Reset Mode**").

#### <3> Slave status initialization

The slave status is initialized as shown in Table 5-5.

| Table 5-5. | Slave Status | after Execution | of INIT Command |

|------------|--------------|-----------------|-----------------|

|------------|--------------|-----------------|-----------------|

| Bit   | Value | Meaning                         |

|-------|-------|---------------------------------|

| Bit 2 | 0     | Unit is not locked.             |

| Bit 0 | 0     | Slave transmit buffer is empty. |

<4> Slave transmission and broadcast reception are enabled.

<5> After the 2-byte command parameter (master address and condition setting code) have been read from the write data buffer (WDB), WDB is cleared.

#### (2) Example

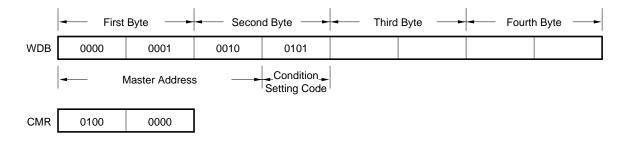

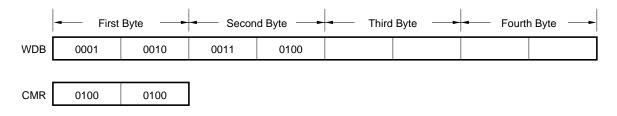

When INIT command specifies that the master address is '012H' and the condition setting are 'communication in mode 1' and 'slave data transmission section operable', the contents of WDB and CMR are as shown below.

#### 5.2.2 SETSA command (command code: 0001)

#### (1) Functions

<1> Slave address (12 bits) setting

The value for the slave address set by the SETSA command remains unchanged until the power is turned off or the reset mode is entered.

<2> This command clears WDB after reading the 2-byte command parameter (slave address) from WDB.

#### (2) Example

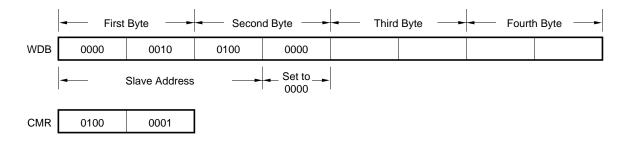

When SETSA command sets the slave address as '024H', the contents of WDB and CMR are as shown below.

#### 5.2.3 MREQ1 command (command code: 0010)

#### (1) Functions

This command executes a master communication (transmission or reception). After execution of the command, the unit begins communication as the master unit. As long as it does not lose in arbitration, the master unit will communicate with the slave unit which has the slave address specified by SETSA command.

<1> Selected broadcast communication or ordinary communication Broadcast communication selection : 0H (broadcast bit '0' output)

- Ordinary communication selection : 8H (broadcast bit '1' output)

- <2> Sets the control bits (4 bits)

- <3> Sets the number of transmit data bytes (8 bits) (transmission only)

| Number of Transmit Data Bytes | Command Parameter |  |  |

|-------------------------------|-------------------|--|--|

| 1 byte                        | 1H                |  |  |

| 2 bytes                       | 2H                |  |  |

| :                             | :                 |  |  |

| :                             | :                 |  |  |

| 255 bytes                     | FFH               |  |  |

| 256 bytes                     | 00H               |  |  |

Table 5-6.

Number of Transmit Data Bytes Setting

<4> Sets the transmit data (transmission only)

#### (2) Example

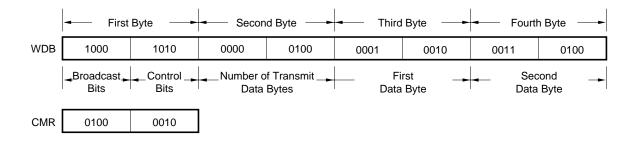

When the MREQ1 command is used to select 'ordinary communication', set the control bit to 'AH' (command write and lock), the number of transmit data bytes to 4, and the transmit data to 12H, 34H, 56H, and 78H, the contents of WDB and CMR are shown below.

# Caution Transmit data 56H and 78H should be set when the above command parameters have been read and WDB is empty.

#### 5.2.4 MREQ2 command (command code: 0011)

#### (1) Functions

This command re-executes a master communication (transmission or reception). If master transmission or reception stops midway, the master communication is re-executed from the stopped condition.

#### (2) Command execution conditions

If a communication control command other than an MREQ2 command is executed after the master communication ends midway, the MREQ1 command may not re-execute the communication correctly from the communication interrupted condition.

#### (3) Example

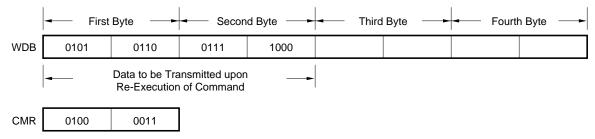

When re-execution is performed by the MREQ2 command when communication has been interrupted due to generation of a timing error after transmission of two bytes (12H and 34H) in mode 1, as in the MREQ1 command example, the contents of WDB and CMR are as shown below.

The previously set MREQ1 command values are used for the broadcast bits, control bits and number of transmit data bytes.

- Cautions 1. A master communication performed by execution of the MREQ1 and MREQ2 commands is performed in only one frame. However, if the unit loses in arbitration, the frame is automatically reset up twice (three times in total).

- 2. INIT command must be executed before setting the MREQ1 or MREQ2 command. If MREQ1 or MREQ2 is set before execution of INIT command, master communication will not be performed.

#### 5.2.5 ABORT command (command code: 0100)

#### (1) Functions

This command aborts master communications and slave unit data transmissions.

- <1> It clears the data placed in WDB.

- <2> It cancels the slave transmit data (SETSD command).

#### (2) Example

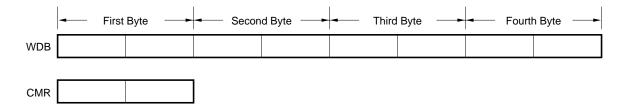

When the master unit begins communication as in the MREQ1 command example, a communication error is generated and the two bytes of transmit data (12H and 34H) remaining in WDB are canceled by ABORT command, the contents of CMR are as shown below.

#### [Before execution of ABORT command]

#### [After execution of ABORT command]

The data placed in WDB is cleared.

#### 5.2.6 SETSD command (command code: 0101)

#### (1) Functions

This command specifies the data transmitted to the master unit when a 'data read and lock' (control bits: 3H) or a 'data read' (control bits: 7H) is received from the master unit.

<1> Sets the number transmit data bytes (8 bits)

| Table 5-7. | Number | of | Transmit | Data | Bytes |

|------------|--------|----|----------|------|-------|

|------------|--------|----|----------|------|-------|

| Number of Transmit Data Bytes | Command Parameter |  |  |

|-------------------------------|-------------------|--|--|

| 1 byte                        | 1H                |  |  |

| 2 bytes                       | 2H                |  |  |

| :                             | :                 |  |  |

| :                             | :                 |  |  |

| 64 bytes                      | 40H               |  |  |

<2> Sets the transmit data

#### (2) Validity of SETSD command

When SETSD command is executed, it remains valid until one of the following cases arises.

- 'Data read and lock' (control bits: 3H) or 'data read' (control bits: 7H) is received from the master unit.

- ABORT command is executed.

- Power is turned off, or the reset mode is entered.

When the SETSD command is valid, WDB functions as the slave transmit buffer.

# Caution The SETSD command can be executed even if the unit is placed in the slave transmission selection halted state by INIT command.

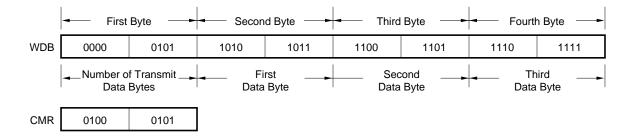

#### (3) Example

When the SETSD command is used to set the number of transmit data bytes to 5, and the transmit data to ABH, CDH, EFH, 14H, and 25H, the contents of WDB and CMR are as shown below.

# Caution Transmit data 14H and 25H should be set when the above command parameters have been read and WDB is empty.

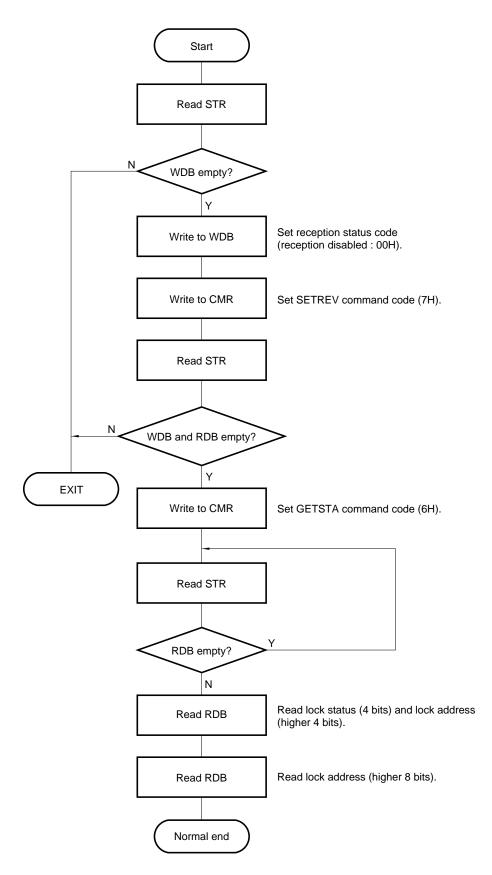

#### 5.2.7 GETSTA command (command code: 0110)

The GETSTA command is used by a unit to check whether it is locked by another unit.

#### (1) Functions

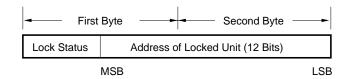

<1> Reads the lock status which indicates whether or not this unit is locked by another unit. '1J' is placed in RDB if the unit is locked, and '0H' if not locked.

<2> The address (12 bits) of a locked unit is placed in RDB. This data is meaningless when the unit is not locked.

After execution of GETSTA command, the data placed in RDB is as follows.

### (2) Command setting conditions